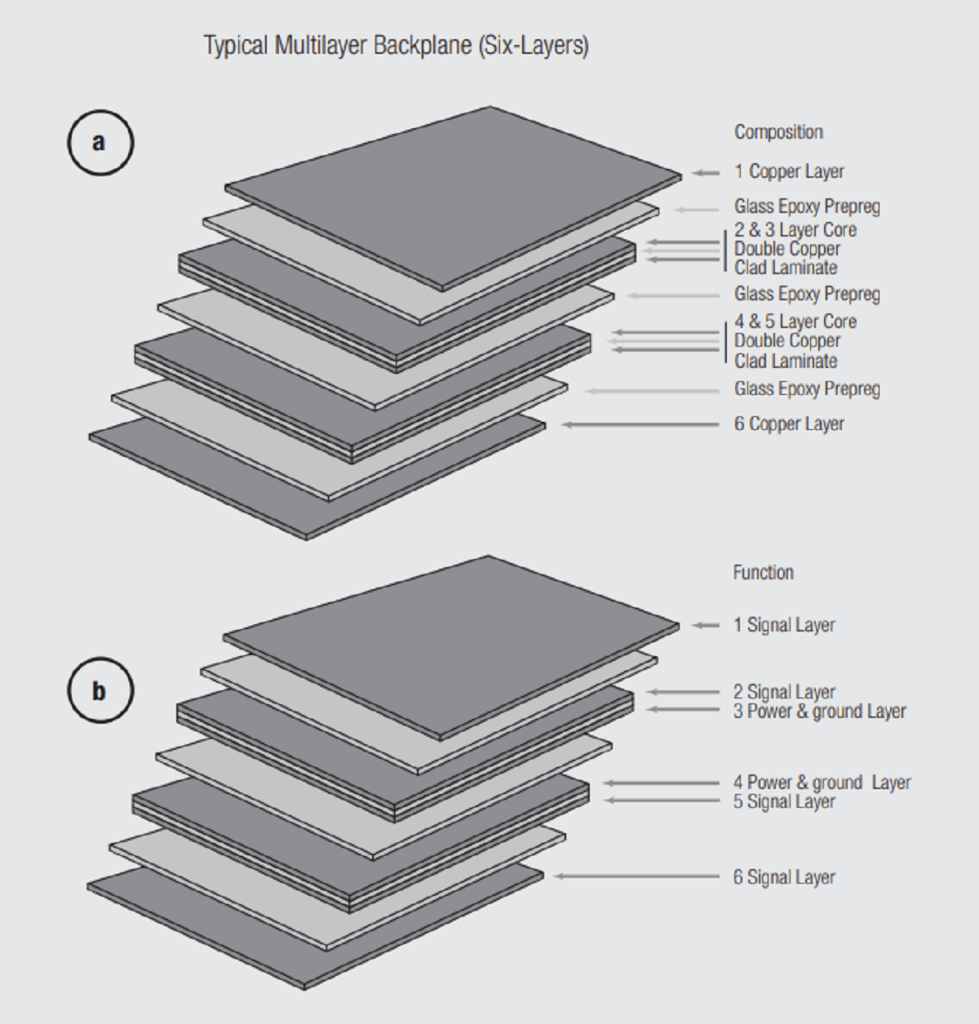

Figure 2.64 schematically illustrates the components of a multilayer PCB prior to laminating. This PCB will have six layers.

Each layer consists of an FR4, fiberglass epoxy substrate with copper circuitry on both sides of the substrate. The thickness and distribution of the copper depends on whether the function of the circuitry is to carry signal currents, milliamps to a few amps, or power, tens of amps. A bonding medium, prepreg, is placed between each pair of layers. In this example, starting from the top, the first layer has signal traces on each side. The second layer has a power/ground plane on each side. The third and fourth layers also have signal traces on each side. In the manufacturing process these four layers and the prepreeg are stacked and laminated under heat and pressure to create a multilayer PCB.

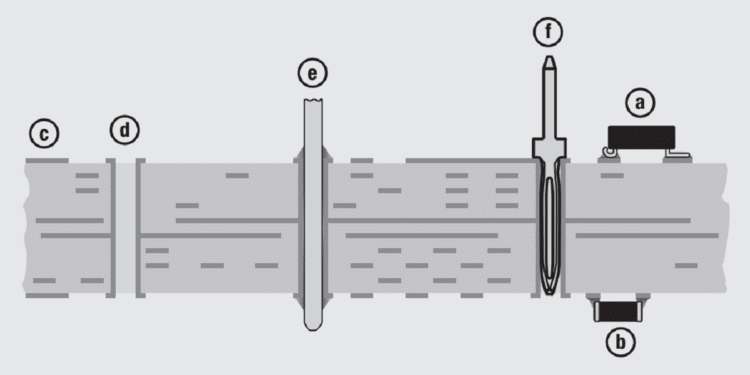

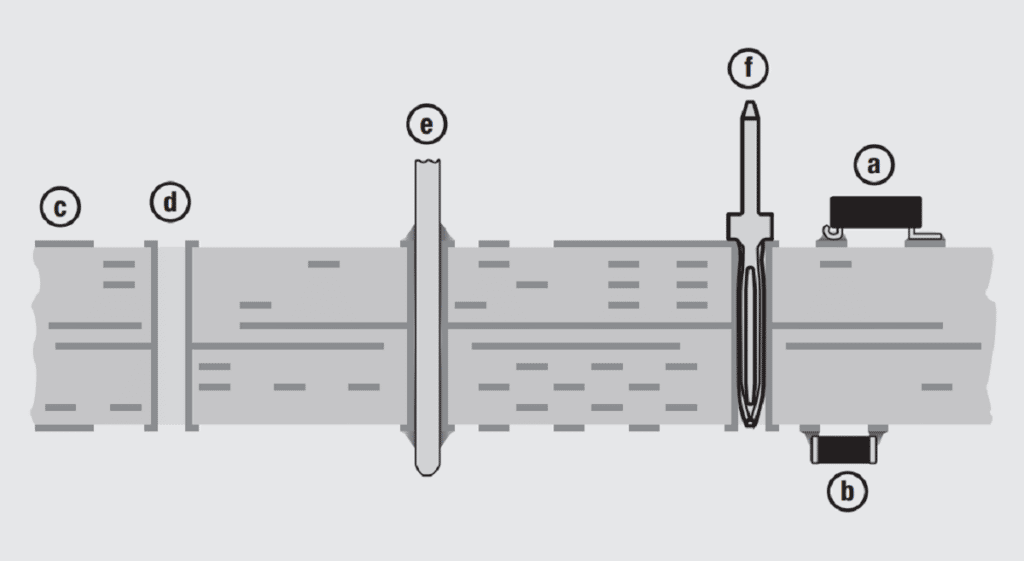

Figure 2.65 illustrates a cross section of the laminated PCB described. The small rectangles shown in the first, third and fourth layers are signal traces that run between the many devices that are mounted on the PCB. The power and ground planes in the second layer are continuous with the exception of holes in the planes to allow inter-connections to be made between the first, third and fourth layer circuitry using Plated Through Holes, PTH, three of which are shown in the drawing.

Consider now the variety of connections, mechanical and soldered, that can be made to this PCB. Note that some of the signal traces are on the surfaces of the PCB. Expanded areas along a surface trace to allow contacts to be made to the trace are called lands or pads. In addition to the copper circuitry, lands require an additional plating with the plating composition and thickness depending on the intended use of the pad, in particular whether mechanical or soldered connections will be made to the land. The plating considerations will be discussed with each application.

The top right component, Figure 2.66a, is soldered to surface pads on the PCB. For convenience, two different lead geometries, J-lead and Gull Wing are shown. In practice, of course, a component will use a single lead style. These geometries are two of the more commonly used methods for providing lead compliance to the soldered connection to minimize the effects of differential thermal expansion stresses on the solder joint as will be discussed in the section on SMT. Similar geometries are used as leads on connectors intended for SMT applications for the same reason. The PCB pads that are to be soldered will generally be treated so as to maintain or provide solderability of the base copper circuitry. Clean copper is readily solderable, but given the tendency of copper to corrode, the copper surface may receive an organic coating or a thin gold plating to prevent such corrosion and maintain the copper solderability. A second approach is to plate the copper with a solderable coating, tin depending on the environmental requirements to be met. The tin coating is generally screened on to the copper and reflowed. The coating thickness is typically of the order of 2 to 4 µm.

The bottom right component, Figure 2.65b, is a flip chip package which is soldered to the surface pads of the PCB using solder bumps or columns, a design sometimes called a leadless package. The plating requirement for this application is essentially the same as discussed for the previous component.

The pads on the left edge of the board, Figure 2.65c, are intended to mate to a card edge connector. The plating on the pad must be compatible with that on the card edge connector which is either gold over nickel or tin. The plating thicknesses on card-edge pads are typically in the range of 0.4–0.8 µm (15 to 30 microinches) for the gold and 1.25 to 2.5 µm (50 to 100 microinches) for the nickel. For tin coatings the thickness will be of the order of 2.5 µm (100 microinches). In addition to card edge connections, Central Processor Units, CPU are also connected to surface lands on multilayer boards. A Land Grid Array, LGA, socket contains spring contacts which are sandwiched between the lands on the PCB and the associated pads on the CPU package. LGA sockets use gold over nickel platings with the thicknesses noted above.

The three PTH connections are all different. As illustrated, Figure 2.65d shows a PTH that is used to make connections between layers within the board. For such applications a copper plating is generally used, the thickness depending on the current requirements to be supported. In this example the press-in solder contact, Figure 2.65e, makes a connection to one of the power/ground planes. A press-in solder pin is generally a solid, rigid pin and exerts only enough force to hold the pin in place until it is soldered, generally wave soldered. In contrast, the compliant press-in pin, Figure 2.65f, is intended to provide a robust mechanical permanent connection without the need for solder.

Two different permanent connection technologies, compliant press-in pins and soldering, have been introduced in this introductory section. Each will now be discussed individually.